# Suppression of DC Link Voltage Fluctuation and Dynamic Response Optimization in Grid-Tied Inverters

### Tianfeng Lan, Jie Yao\*, Guixiang Huang

Shanghai Testing and Inspection Institute for Electrical Equipment Co., Ltd., Shanghai, China \*Corresponding Author

Abstract: During operation, the DC bus in single-phase power conversion systems inevitably generates double-frequency voltage ripple. To address the issue of current reference tracking accuracy, it is common practice in engineering to embed notch filters within the control algorithm. However, traditional solutions suffer from inherent drawbacks such as sluggish dynamic response and a tendency for system oscillations. This paper innovatively proposes a real-time computational algorithm based on system parameters to identify the second harmonic voltage component. This approach requires neither modifications to the main circuit topology nor additional filtering stages in the voltage loop. By redesigning the voltage outer loop controller structure, the dynamic response characteristics of the system are significantly enhanced, effectively suppressing overshoot during voltage regulation. Combined with a current inner loop control strategy employing a quasi-proportional resonant regulator, the constructed dual closed-loop control system achieves excellent dynamic performance and stability while maintaining precision. steady-state Simulation results based **MATLAB** on /Simulink confirm the feasibility superiority of the proposed control scheme.

Keywords: Harmonic Voltage Identification; Dual Closed-loop Control; Quasi-Proportional Resonant Control; Dynamic Performance; Second Harmonic Suppression

### 1. Introduction

Single-phase inverters, serving as core components in power electronic systems, play an indispensable role in critical fields such as renewable energy generation, industrial drives, and uninterruptible power supplies [1-2]. With the ongoing global energy transition and continuous innovation in power electronics

technology, modern power systems are imposing increasingly stringent performance requirements inverters. These diverse industrial applications demand not only precise control of voltage, current, and power but also excellent dynamic response characteristics and steadystate performance under complex operating conditions, while simultaneously requiring compliance with rigorous technical specifications including high efficiency, high density, and low electromagnetic interference. Particularly driven by current carbon neutrality goals, single-phase inverters must also demonstrate higher levels of intelligence and enhanced grid adaptability to meet the construction needs of future smart grids. However, single-phase inverters consistently face a long-standing technical challenge during significant twice-line-frequency operation: harmonic components with considerable amplitude are generated on the DC bus due to the inherent instantaneous power pulsation characteristics of single-phase systems [3-4]. The physical essence of this problem lies in the inherent periodic fluctuation of power transfer in single-phase systems. The mathematical model established by Jiang et al. [5] provides in-depth theoretical analysis and quantitative research on this phenomenon, clearly identifying this power pulsation characteristic as the fundamental cause of current and voltage ripple at twice the line frequency on the DC side. If these harmonic components are not effectively suppressed, they can exert multiple adverse effects on the system's output characteristics through the control loop, leading not only to output waveform distortion and degraded power quality but also potentially causing electromagnetic interference issues, increasing system losses, and reducing conversion efficiency. Particularly noteworthy is the systematic experimental validation by Zhou et al. [6], which demonstrates that such second-harmonic components may induce system resonance under specific

conditions. When system impedance characteristics match the harmonic frequency, resonance phenomena occur, causing a sharp increase in harmonic amplitude that further amplifies the threat to system stability, presenting severe challenges to the secure operation of the system.

To address the issue of second-order harmonics on the DC side, the academic community has proposed various solutions, which can be broadly categorized into two technical pathways: suppression methods based on improvements in hardware topology and suppression strategies based on optimization of control algorithms. In terms of hardware improvements, Alsolami et al. [7] proposed a design scheme using auxiliary circuits, which constructs a harmonic current path by adding an LC filter network, but this method significantly increases system volume and cost; Li et al. [8] introduced a differential capacitor solution that achieves complementary capacitor voltage ripple, yet due uncontrollable intervals in the algorithm, it cannot achieve full-cycle effective suppression. In the field of control algorithm optimization, Somkun et al. [9] employed a notch filter for harmonic suppression, but it introduces phase lag issues; Ahangarkolaei et al. [10] applied predictive control to harmonic suppression, achieving notable results but exhibiting sensitivity to parameter variations; and for twosingle-phase inverters, the virtual fractional-order inductance control proposed by Zhou et al. [11-12] effectively eliminates second-order harmonic current but inevitably reduces the system's dynamic response performance.

Building on an in-depth analysis of existing control strategies, this paper proposes a composite control strategy combining quasiproportional resonant control with an improved voltage feedforward method. This solution first establishes an accurate mathematical model of the system to analyze the generation mechanism and propagation path of the second-order harmonics. Subsequently, a quasi-proportional resonant controller is adopted for the inner current loop, leveraging its high-gain characteristics at the fundamental frequency to achieve precise tracking of reference signals. Meanwhile, a harmonic extraction algorithm based on instantaneous power calculation is introduced into the outer voltage loop to estimate the second-order harmonic components in real

time and implement feedforward compensation.

## 2. Traditional Control Strategy

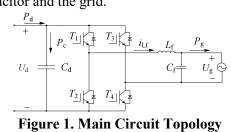

The main circuit of a single-phase inverter is shown in Figure 1, where U<sub>d</sub>, P<sub>d</sub>, and C<sub>d</sub> represent the DC-side voltage, power, and filter capacitor respectively; the AC filter inductor and capacitor are L and C, and the grid voltage is Ug; P<sub>c</sub> and P<sub>g</sub> indicate the power flowing through the capacitor and the grid.

Figure 1. Main Circuit Topology

### 2.1 Current Inner Loop Design

To enhance the stability and anti-interference performance of the control system, this paper adopts a quasi-PR regulator as the current loop controller with the following transfer function:

$$T_{PR}(s) = k_{p} + \frac{2k_{r}\omega_{t}s}{s^{2} + 2\omega_{t}s + \omega_{p}^{2}}$$

(1)

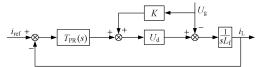

where  $k_p$  is the proportionality coefficient,  $k_r$  is the resonance coefficient,  $\omega_n$  is the fundamental angular frequency, and  $\omega_t$  is the cutoff frequency,  $\omega_t = 5 \text{ rad/s}, k_p = 0.015, k_r = 8, \text{ and } \omega_0 = 2\pi f_0 = 100\pi.$ The inner current loop is shown in Figure 2, where  $K = 1/U_d$ .

Figure 2. Current Inner Loop Control

### 2.2 Voltage Outer Loop Design

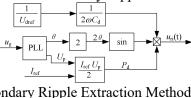

The control block diagram of the outer voltage loop is shown in Figure 3, where U<sub>dref</sub> is the voltage reference setpoint,  $k_{dc}$  and  $\tau$  are the Pregulator parameters, G<sub>c</sub>(s) is the closed-loop transfer function of the inner current loop.

Figure 3. Voltage Outer Loop Control

#### 3. Improved DC Voltage Control Strategy

### 3.1 Control Strategy

The time-domain characteristics of the DC bus

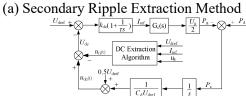

voltage can be described by Equation 3, where  $u_{ri}$  (t) represents the second-harmonic voltage ripple. Given the inherent double-frequency ripple characteristic in the DC bus voltage and its measurability, the estimated value of the ripple component can be obtained through analytical methods:

$$U_{d} = u_{d}(t) - u_{ri}(t)$$

$$= u_{d}(t) - \frac{P_{d}}{2\omega C_{d}U_{dref}} \sin 2\theta$$

(2)

If system losses are ignored,  $P_d$  is equal to  $P_g$ . The current loop can rapidly and accurately track the system's output value. When the grid-side current reference amplitude  $I_{\rm ref}$  is used to characterize the actual grid-side current, and the voltage amplitude  $U_p$  from the phase-locked loop is employed to represent the actual grid-side voltage, the following relationship can be established:

$$P_{\rm d} = \frac{U_{\rm p} I_{\rm ref}}{2} \tag{3}$$

Based on the aforementioned analysis, the second harmonic component in the DC voltage can be extracted using the algorithm illustrated in Figure 4(a), with its implementation structure shown in Figure 4(b). By injecting a compensating signal with opposite phase to this second harmonic into the voltage outer-loop control, the harmonic fluctuation in the DC bus voltage can be effectively suppressed.

(b) Voltage Loop Control Diagram

Figure 4. Improved DC voltage

Figure 4. Improved DC voltage Control Strategy

#### 3.2 Parameter Design

Based on the block diagram presented in Figure 4, the characteristic equation for the complete control loop utilizing the proposed improved algorithm can be derived as:

$$1 - k_{\rm dc} \frac{U_{\rm g}}{2C_{\rm d}U_{\rm dref}} \left(1 + \frac{1}{\tau s}\right) \frac{1}{s} G_{\rm c}(s) = 0$$

(4)

The closed-loop transfer function is:

$$G_{u}(s) = \frac{\frac{1}{C_{d}U_{dref}} \frac{1}{s}}{1 - k_{dc} \frac{U_{g}}{2C_{d}U_{dref}} \left(1 + \frac{1}{\tau s}\right) \frac{1}{s} G_{c}(s)}$$

(5)

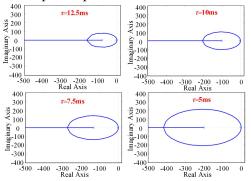

To optimize the suppression of DC bus voltage fluctuations, it is theoretically necessary to reduce the value of  $\tau$  to extend the voltage outer loop bandwidth. A root locus analysis was performed based on Equation (4) for four parameter configurations:  $\tau=12.5 \mathrm{ms}$ , 10 ms, 7.5 ms, and 5 ms. Figure 5 demonstrates that as the value of  $\tau$  decreases, the system remains stable while the intersection point of the root locus with the real axis gradually shifts leftward. Taking into account both dynamic performance and stability,  $\tau=5 \mathrm{ms}$  was ultimately determined to be the optimal parameter.

Figure 5. Root Trajectories of the Improved Control Algorithm for Different Values of  $\tau$

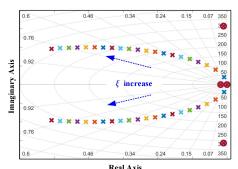

When the damping ratio  $\xi$  varies within the range of 0.1 to 0.8, the value of the controller parameter k<sub>dc</sub> significantly influences the dynamic response characteristics of the system. The pole-zero distribution of the improved control algorithm model constructed based on Equation (5) is shown in Figure 6. Simulation results indicate that as the value of  $\xi$  increases, the dominant poles of the system continuously migrate toward the left half-plane, while the corresponding  $k_{dc}$ parameter exhibits monotonically increasing characteristic. It should be noted that excessively high k<sub>dc</sub> values amplify high-frequency system noise, adversely affecting the practical implementation of the controller. Furthermore, to ensure sufficient damping capability in the high-frequency range, the value of  $\xi$  should not be set too low. Through comprehensive optimization,  $\xi = 0.707$  was selected as the optimal operating point, with a corresponding  $k_{dc} = 0.21$ . Under this parameter combination, the calculated system overshoot using the higher-order system approximation method is 11.3%, with a settling time of 23 ms.

Figure 6. Closed-Loop Zero-Pole Distribution

# 4. Experimental Verification

To validate the control performance of the improved DC bus voltage extraction algorithm, this study established a numerical model of a single-phase H-bridge converter MATLAB/Simulink environment, with specific experimental parameters provided in Table 1. The algorithm was evaluated through two typical operational scenarios: first, examining the system dynamic response characteristics through step changes in the DC voltage reference; second, analyzing the voltage outer-loop response and grid-connected current characteristics stability under step disturbances in grid-side power.

**Table 1. Experimental Platform Parameters**

| Tuble It Experimental I late of in I arameters |                  |                |

|------------------------------------------------|------------------|----------------|

| Variable Name                                  | Variable symbol  | Variable value |

| switching frequency                            | $f_{\mathrm{w}}$ | 10kHz          |

| grid frequency                                 | $\mathbf{f}_1$   | 50Hz           |

| DC bus voltage                                 | $U_d$            | 400V           |

| RMS grid voltage                               | $U_g$            | 220V           |

| filter inductors                               | $L_{\mathrm{f}}$ | 0.6mH          |

| filter capacitor                               | $C_{\mathrm{f}}$ | 10uF           |

| DC-side capacitance                            | $C_d$            | 220uF          |

#### 4.1 DC Voltage Step Test

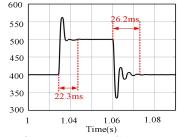

Figure 7 illustrates the first experimental scenario, where the DC bus voltage undergoes step-up transitions from 400V to 500V and step-down transitions from 500V to 400V. The measured settling times of the improved algorithm during voltage ascent are 22.3ms and 26.2ms, showing good agreement with the theoretical calculation of 23ms.

Figure 7. DC Bus Voltage Step Response Test

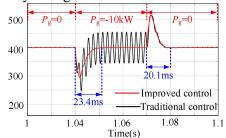

As shown in Figure 8, the second experimental scenario involves step changes of grid-side output power between 0kW and 10kW to verify the system's suppression capability against double-frequency ripple in the DC bus voltage and its dynamic response characteristics. The 10kW grid-side power output is achieved by connecting a  $16\Omega$  load to the DC side while maintaining a stable DC bus voltage of 400V. Experimental results demonstrate that the improved algorithm yields settling times of 23.4ms and 20.1ms during power step-up phases, consistent with the theoretical value of 23ms. Comparative analysis with the baseline control strategy confirms that the proposed improved control method effectively suppresses doublefrequency voltage oscillations on the DC side.

Figure 8. Grid-Side Power Step Test

## 5. Conclusion

This research systematically investigates the performance optimization of single-phase gridconnected inverter systems and proposes an improved DC bus voltage control method based the conventional double-loop control architecture. Within this control framework, the current inner loop specifically employs a quasiproportional resonant controller, whose strategic design aims to achieve precise and reliable reference signal tracking while effectively enhancing the system's overall stability margin and dynamic response performance. To address the inherent technical challenge of doublefrequency ripple in the DC bus voltage commonly found in traditional control schemes, an innovative DC bus voltage extraction algorithm has been meticulously designed and implemented through advanced digital signal processing techniques. Comprehensive theoretical analysis and extensive experimental results demonstrate that the newly proposed algorithm offers dual advantages: it not only effectively suppresses the second-harmonic components present in the voltage outer loop but also enables the control system to achieve excellent dynamic response speed through

systematic parameter optimization. Furthermore, detailed simulation studies and rigorous experimental validation collectively indicate that the proposed control strategy consistently demonstrates excellent steady-state operating outstanding characteristics and dynamic performance metrics, thereby clearly confirming its technical correctness and engineering practicality in practical applications. Ultimately, the research findings and methodological contributions hold significant theoretical value and provide valuable engineering guidance for substantially enhancing the operational performance and reliability of single-phase gridconnected inverters in practical industrial applications.

#### References

- [1] Li Z, Zhu M, Hou C, et al. Impedance Modelling Mechanisms and Stability Issues of Single Phase Inverter with SISO Structure and Frequency Coupling Effect. IEEE Transactions on Energy Conversion, 2022, 37 (1): 573-584.

- [2] Silva R D P, Silveira D B, Barros R C, et al. Third-Harmonic Current Injection for Wear-Out Reduction in Single-Phase PV Inverters. IEEE Transactions on Energy Conversion, 2022, 37 (1): 120-131.

- [3] Liu B, Li G, He D, et al. DC and AC Power Quality Control for Single-Phase Grid-Tied PEMFC Systems with Low DC-Link Capacitance by Solution-Space-Reduced MPC. IEEE Transactions on Industrial Electronics, 2022, 69 (6): 5625-5636.

- [4] Karimi E, Tehrani B M, Adib E. A Soft-Switching Double-Input Micro-Inverter. IEEE Transactions on Industrial Electronics, 2021, 68 (8): 6721-6728.

- [5] Jiang S, Liu Y. EMI Noise Reduction for the Single-Phase Grid-Connected Inverter with a Modified Harmonic Filter Design. IEEE

- Transactions on Electromagnetic Compatibility, 2021, 63 (3): 739-751.

- [6] Zhou H, He L, Lin Z. Low Frequency Current Ripple Suppression for Two-Stage Single-Phase Inverter Based on Impedance Editing. IEEE Transactions on Industrial Electronics, 2022, 69 (12): 13417-13427.

- [7] Alsolami Mohammad F, Potty Kapil A, et al. Mitigation of Double-Line-Frequency Current Ripple in Switched Capacitor Based UPS System. IEEE Transactions on Power Electronics, 2021, 36 (4): 4042-4051.

- [8] Li Z, Zhu M, Hou C, et al. A Second Harmonic Suppression Method Based on Differentiated-Capacitance Design for Input-Parallel Output-Series DAB Fed Single-Phase VSI. IEEE Transactions on Power Electronics, 2022, 37 (10): 11592-11606.

- [9] Somkun S, Srita S, Kaewchum T, et al. Adaptive Notch Filters for Bus Voltage Control and Capacitance Degradation Prognostic of Single-Phase Grid-Connected Inverter. IEEE Transactions on Industrial Electronics, 2023, 70 (12): 12190-12200.

- [10]Ahangarkolaei Javad M, Izadi M, Nouri T, et al. Applying Sliding Mode Control to Suppress Double Frequency Voltage Ripples in Single-phase Quasi-Z-source Inverters. CSEE Journal of Power and Energy Systems, 2023, 9 (2): 671-681.

- [11]Zhou H, He L, Lu F. Impedance Editing Based Second Harmonic Current Reduction for New Energy Access System. IEEE Transactions on Industrial Electronics, 2024, 71 (3): 2638-2649.

- [12]Zhou H, He L, Yang Z, et al. Virtual Fractional-Order-Inductor Based Second Harmonic Current Suppression Method. IEEE Transactions on Industrial Electronics, 2024, 71 (8): 8949-8959.